Here are learning tools to help you learn how to design, develop, and optimize RISC-V-based systems. These tools include simulators, debuggers, compilers, and development boards. Simulators and emulators allow users to simulate RISC-V processors and test their designs without the need for physical hardware. Debuggers can help identify and fix errors in RISC-V programs, while compilers can translate high-level code into RISC-V assembly code. Development boards, such as the HiFive1 and the Arty A7, provide a physical platform for users to experiment with RISC-V and develop their own applications.

Trireme

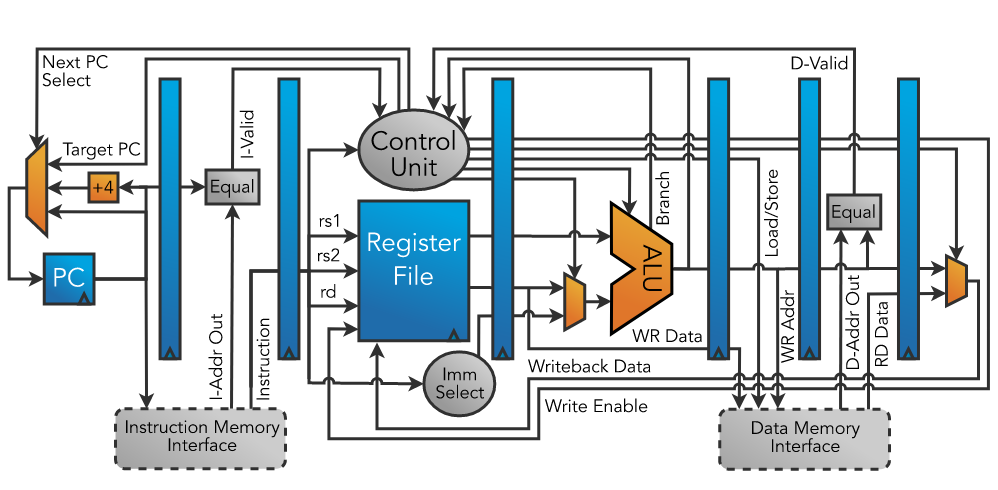

Trireme is a parameterized and synthesizable set of modules for design exploration using the RISC-V ISA. The toolbox includes processors and tools to support them.

Trireme is designed for students and researchers experimenting with the RISC-V ISA features to build fully working architectures and add extensions.

The Trireme Platform includes everything you need to bring up the hardware and software of a custom RISC-V system, from ultra-low-power microcontrollers to high-performance multi-core processors.

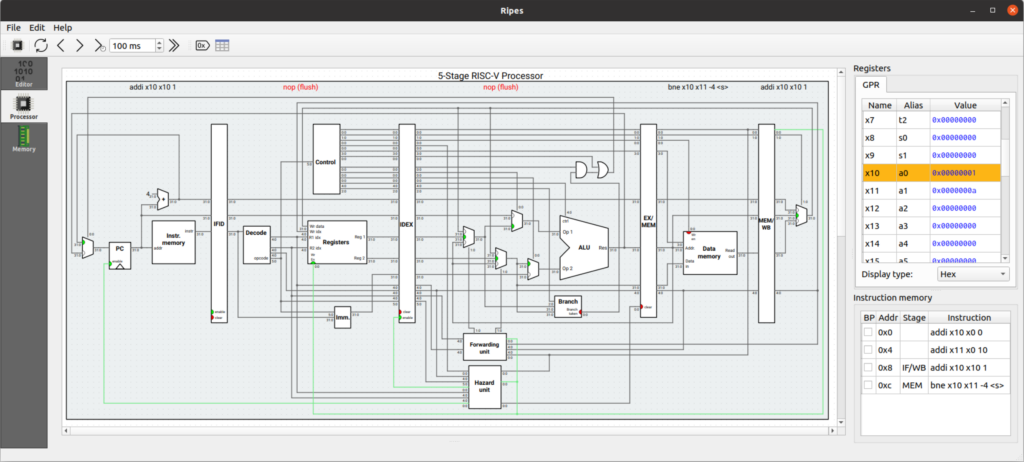

Ripes

Ripes is a visual computer architecture simulator built around the RISC-V ISA. The main feature of Ripes is its tight integration of a built-in assembler, compiler support, and cache simulator; all centered around a visual microarchitecture simulator.

Several microarchitectural models are provided to explore the evolutions of a typical processor pipeline, such as the different iterations of processors when going from a single-cycle model to a classic RISC five-stage pipeline.

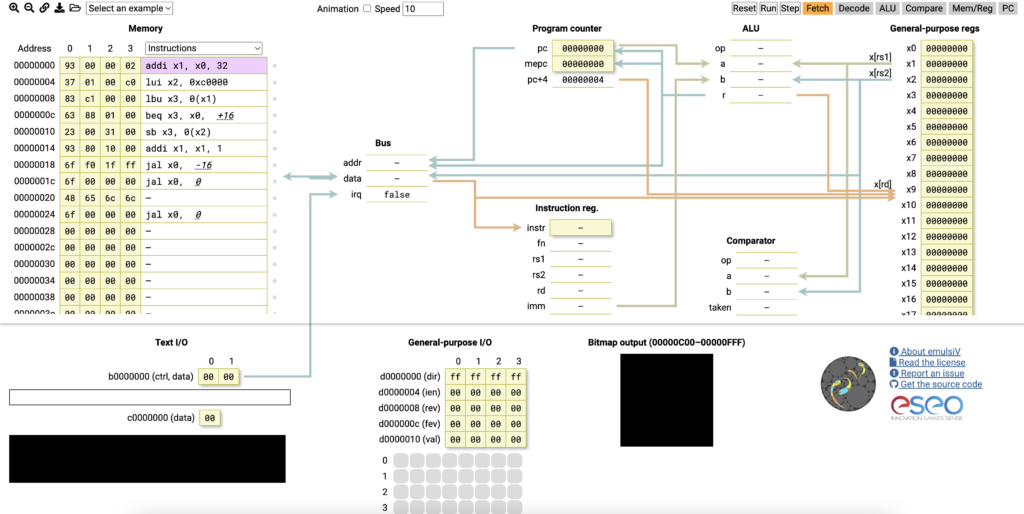

emulsiV

emulsiV is a visual simulator for Virgule, a minimal CPU core implementation based on the RISC-V architecture. This simulator is intended to be used as a tool for teaching the basics of computer architecture.

The user interface shows the structure of the datapath and animates the data transfers between functional units. The execution of a single instruction is decomposed into several steps (fetch, decode, ALU, mem/reg, PC) for educational reasons, but the intent is not to reflect a specific sequencer or pipeline implementation. In fact, we don’t plan to simulate a pipeline in more detail.

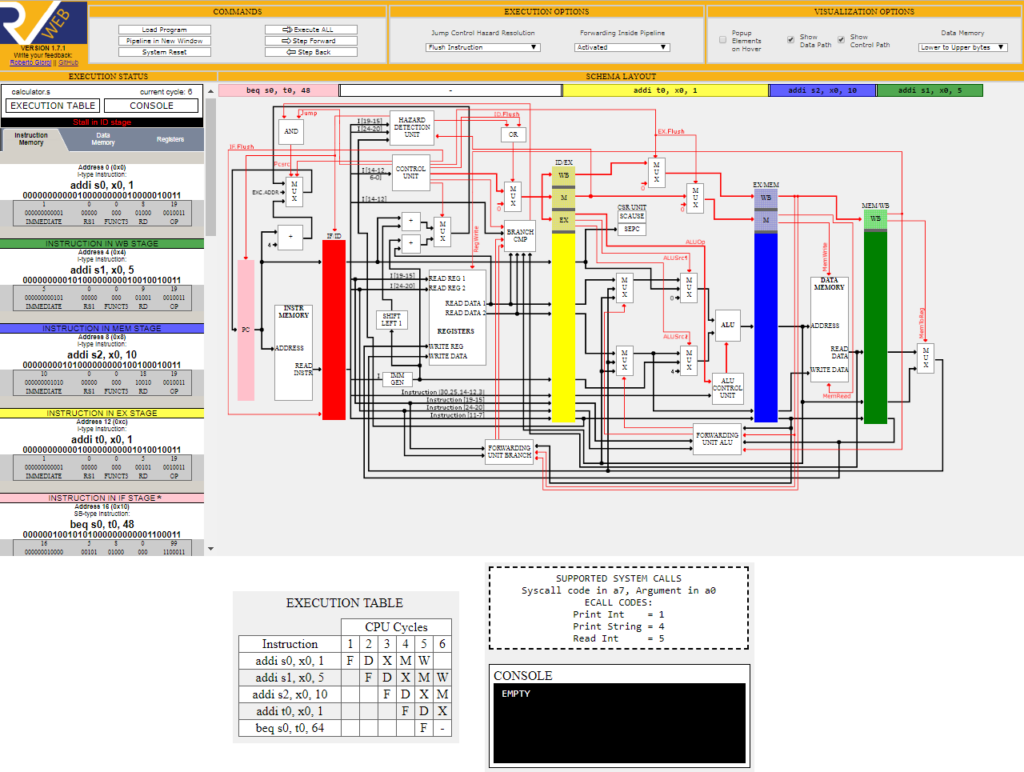

WebRISC-V

WebRISC-V is a web-based graphical pipelined datapath simulation environment built for the RISC-V instruction set architecture. It is suitable for teaching how assembly-level code is executed on the RISC-V pipelined architecture and for illustrating the Pipeline Architectural Elements.

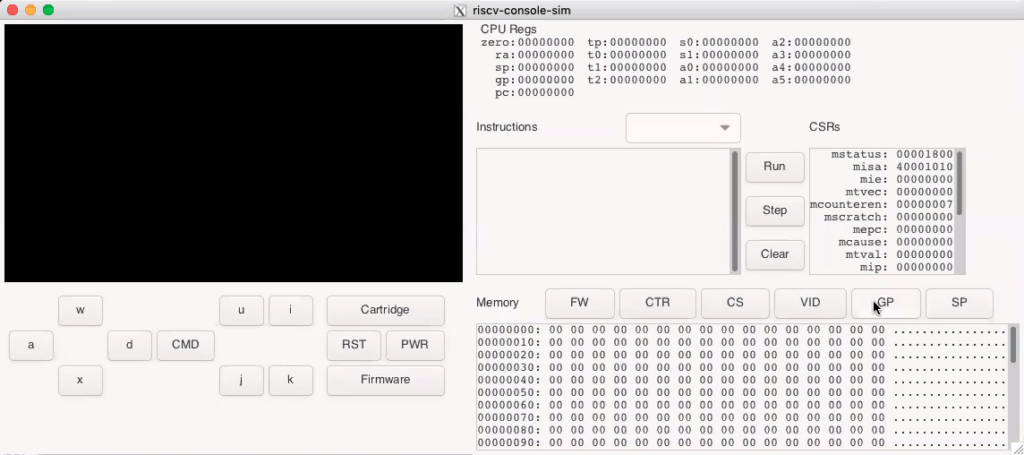

RISC-V Console Simulator

The RISC-V Console is a simulator for a hypothetical RISC-V based game console. The repository provides Dockerfiles to build the necessary RISC-V toolchain for firmware and/or “game” development. The simulator was developed for use in UC Davis’ Computer Science courses; however, any other educators are highly encouraged to take this repository and modify it to meet the needs of your class.

Interpreters

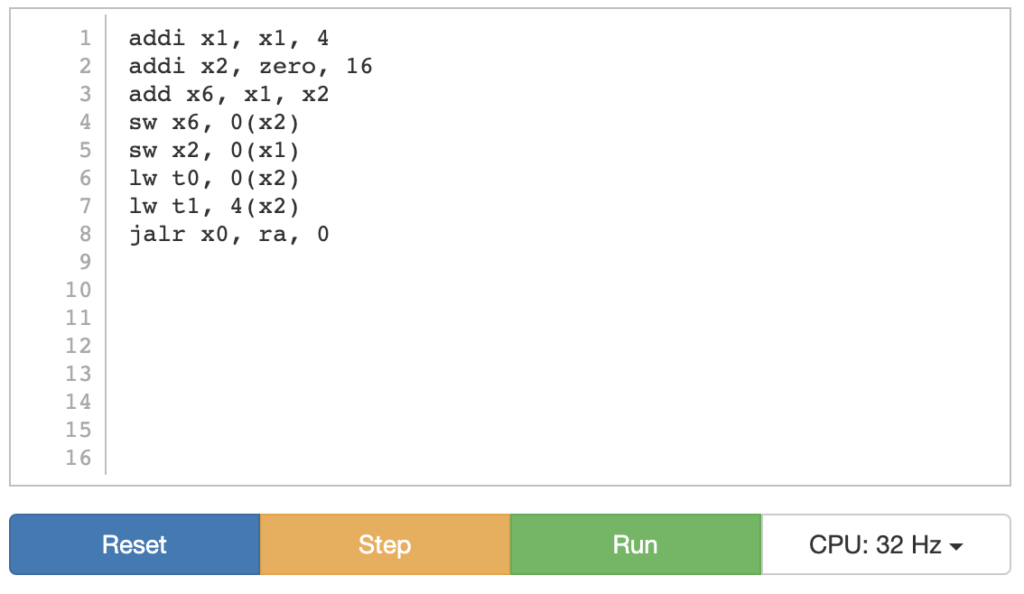

RISC-V Interpreter

A simple RISC-V Interpreter from Cornell University.